日本东京工业大学和青井电子株式会社(AOI Electronics)等组成的研究团队把多个功能不同的多个半导体芯片连接起来,使其像单个芯片一样工作。这样容易提高芯片的集成密度和电气特性,改善成品率。在目前半导体微细化工艺接近极限的情况下,该技术作为替代微细化工艺来提高半导体性能的一种方法而被受期待。

利用新开发的小芯片集成技术试制的样品

多年来,半导体一直按照约两年性能翻一番的“摩尔定律”进化。其原动力是减小构成半导体芯片的晶体管尺寸、提高集成度的微细化工艺技术。

但半导体的细微化工艺正在迎来其极限。美国苹果公司9月发售的智能手机“iPhone”的最新机型采用了线宽为4nm(1nm为10-9m)的半导体芯片。考虑到物理上的极限,全球能制造这种最尖端半导体芯片的企业仅有台积电、三星电子等少数几家。

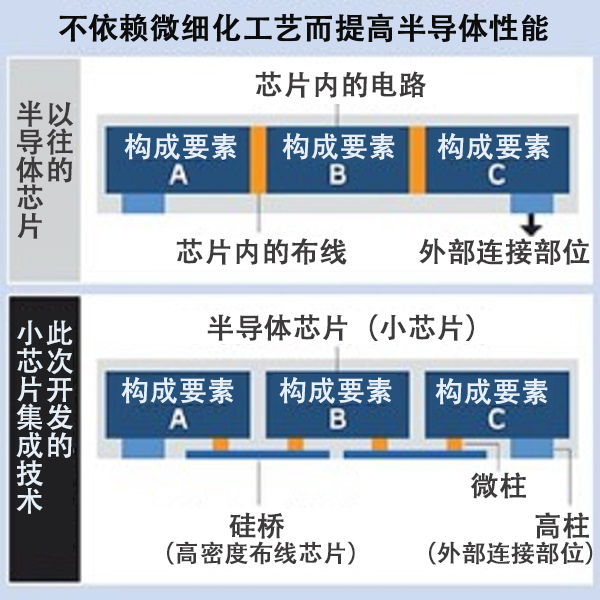

在此背景下,作为新的重点技术而备受瞩目的就是基于“小芯片”(chiplet)的集成技术。这种技术做法不是将所有的半导体电路都集成在一个芯片上,而是将各功能要素单独制造成小芯片,然后像积木那样相互组合——以电信号方式连接多个小芯片,使其像一个大型芯片一样工作。

利用这种方法,可以用最先进的工艺制造图像处理等要求高运算能力的电路,用上一代工艺制作输入输出电路等。与依赖工艺微细化的现有方法相比,在成品率和成本上更具优势。

研究团队此次开发的是,能够以比之前更简单地配置与连接小芯片的技术。连接小芯片之间的硅桥(高密度布线芯片)和多个小芯片利用模塑树脂(mold resin)封装。小芯片和硅桥通过被称为“微柱”的微小金属柱实现电连接。然后使用较大的金属柱(高柱)贯穿模塑树脂,将小芯片的集合体与外部连接。

以往,为了连接芯片彼此,多使用名为“插入层”(interposer)的中间基板。插入层大多用硅来制造,但在气特性、对位精度、成本等方面都还存在课题。

此次新技术的优点是能够以最小限度的要素实现小芯片之间以及小芯片与外部之间的连接。小芯片的集成密度容易提高,容易改善电特性,连接部的对位也变得容易。还具有能提高小芯片与外部电连接布线的高频特性以及散热性能的优点。

今后将致力于提高小芯片的集成规模、验证可靠性等实用化方面的课题。主导这项研究的东工大特任教授栗田洋一郎表示:“首先在日本确立技术,然后向海外拓展。”

为了具体实现上述设想,以东工大、大阪大学、东北大学为中心,有30家左右企业参加的“小芯片集成平台联盟”于2022年10月成立。除了从事半导体和电子零件业务的青井电子之外,还有住友电气工业公司等企业。为开发小芯片集成技术,日本的产学研力量开始集结。

就全球范围来看,2022年3月有10家企业围绕小芯片技术开展了合作,除了英特尔、台积电、高通等半导体企业外,还有谷歌、微软等IT巨头。这些公司成立了标准化和生态联盟,公开了芯片连接方式的开放标准“UCIe”。该领域在全球范围内竞争也很激烈,栗田特任教授指出“日本在半导体材料和制造装置方面实力很强,都能在小芯片技术中发挥作用。小芯片的普及对日本半导体行业来说是一个机会。”

日文:松元则雄、《日经产业新闻》、2022/11/2

翻译:JST客观日本编辑部