东京大学生产技术研究所的小林正治副教授与奈良先端科学技术大学院大学的浦冈行治教授等人组成的联合研究团队,开发出了利用原子层沉积(ALD)法取代常规溅射法成膜氧化物半导体氧化铟(In2O3)的技术,并成功开发出了三维垂直沟道型铁电和反铁电的晶体管存储器。

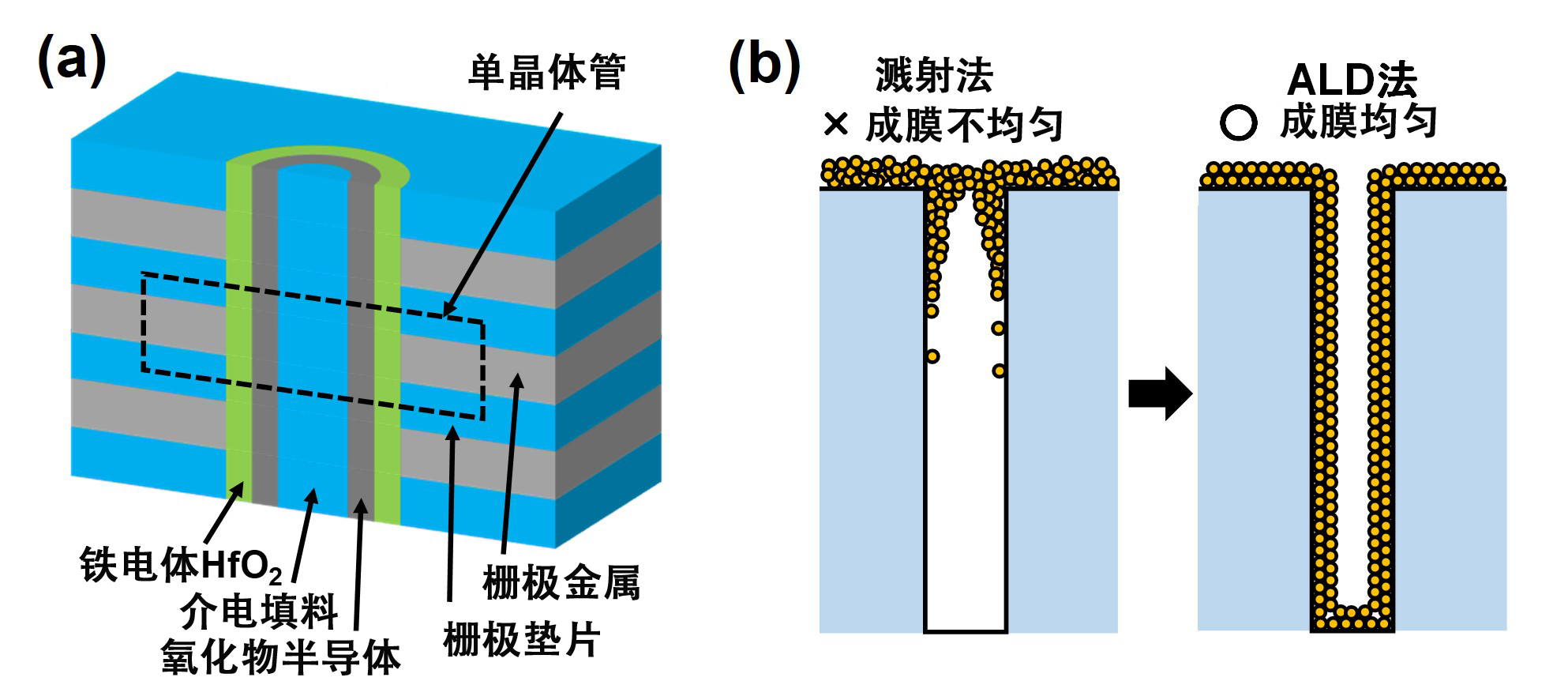

图1:(a)此次提出的使用氧化物半导体作为沟道的三维垂直沟道型FeFET的模式图。栅极绝缘膜使用铁电材料HfO2。(b)氧化物半导体三维成膜时存在的问题和解决方法。通过使用ALD法,可以均匀形成三维结构薄膜。(供图:东京大学生产技术研究所副教授 小林正治教授)

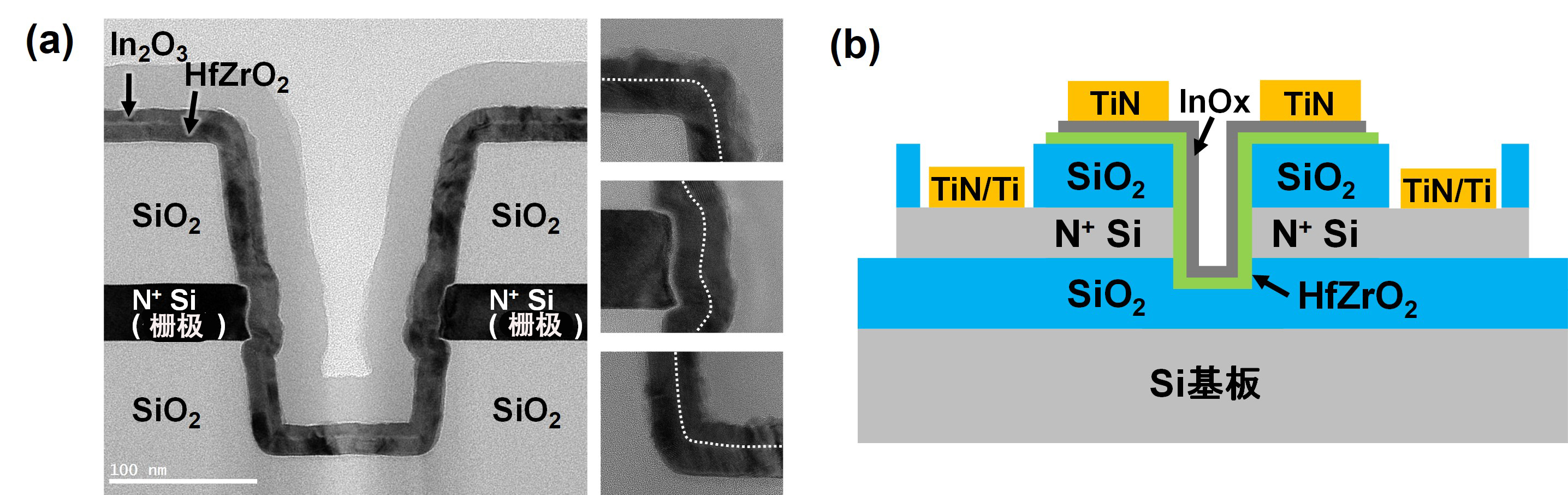

图2:(a)试制的三维垂直沟道型FeFET的截面透射电子显微镜(TEM)照片。铁电材料HfO2和氧化物半导体In2O3都均匀成膜。(b)试制的原型器件整体的截面模式图。(供图:东京大学生产技术研究所副教授 小林正治教授)

随着大数据越来越多地得到应用,不仅是云服务器,IoT边缘器件也需要大容量低功耗的存储器。因此,研究团队着眼于铁电晶体管(FeFET)存储器,通过用原子层沉积法成膜以前大多通过溅射法成膜的氧化物半导体,开发出了三维垂直沟道型FeFET。另外,还开发了可以更有效地进行重写的反铁电晶体管(AFeFET)存储器。

利用通过ALD法成膜的In2O3制作的薄膜晶体管显示出每平方厘米超过40Vs的高迁移率。另外,研究团队还利用ALD法将In2O3均匀形成了三维结构薄膜。并且利用该成膜技术,试制了也可以同样用ALD法成膜的二氧化铪锆(HfZrO2)铁电材料为栅极绝缘膜的FeFET,验证结果显示,如理论预测一样,具有1.5V左右的存储窗口(阈值电压差)、10的4次方以上的重写耐性和10的3次方秒以上的保持特性。

此外,研究团队还提出了一种使用反铁电ZrO 2作为栅极绝缘膜的反铁电晶体管(AFeFET)。氧化物半导体为N型半导体,虽然容易诱导作为多数载流子的电子,但不容易诱导作为少数载流子的空穴,因此特点是,相对于程序状态来说,擦除状态的保持特性容易劣化。通过使用反铁电材料,即使不诱导少数载流子,也能有效执行擦除操作,可以改善擦除状态的保持特性。研究团队经过验证确认,实际具有0.7V左右的存储窗口、10的4次方以上的重写耐性和10的3次方秒以上的保持特性。

小林副教授表示:“这种存储器件技术密度高、功耗低,因此通过应用于IoT器件的存储器,有望开展使用大数据的社会服务。为实现更高的集成度和可靠性,今后将推进器件设计及材料和工艺开发,目标是为IoT边缘器件配备大容量存储器。”

【词注】

■原子层沉积(ALD)法:传统的化学气相沉积法之一。在短时间内将反应前驱体以脉冲方式送入反应室,并使其在成膜晶圆上进行单分子层饱和,然后以脉冲方式在短时间内供应作为氧化剂的水和氧等,使饱和的分子层氧化,形成原子层氧化物。通过重复这个过程可以在每个原子层上成膜。特点是,不仅是平面成膜,三维结构也可以实现负载效应较小的均匀成膜。

原文:《科学新闻》

翻译编辑:JST客观日本编辑部

【论文信息】

期刊:2022 IEEE Silicon Nanoelectronics Workshop

论文:A Vertical Channel Ferroelectric/Anti-Ferroelectric FET with ALD InOx and Field-Induced Polar-Axis Alignment for 3D High-Density Memory

URL:snw2022.conf.nycu.edu.tw/