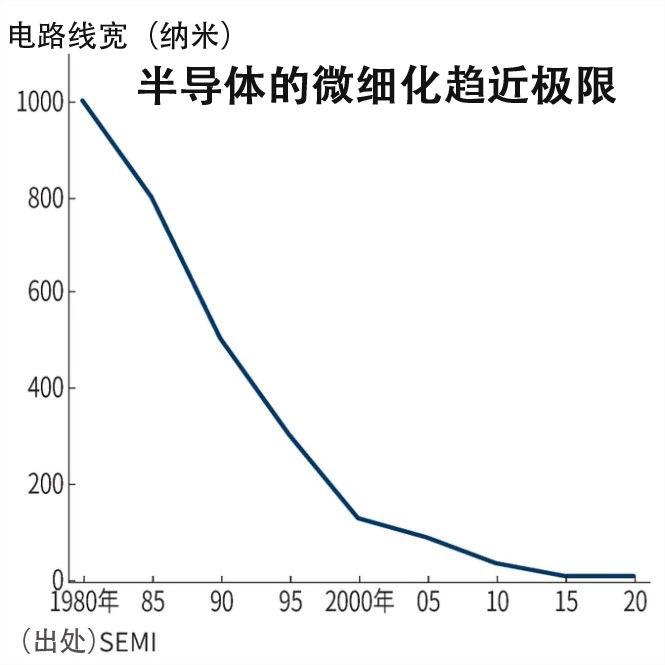

半导体的微细化进程的一些现象显示快要触及“极限”了。智能手机等最先进终端已经开始使用4纳米(纳米为10亿分之1米)产品和5纳米产品。基于微细化的性能和集成度的提升是否很快就会达到极限?记者就此采访了曾在企业从事半导体开发的东京工业大学若林整教授。

东京工业大学的若林整教授

——各公司的最先端产品目前情况如何?

“韩国三星电子的4纳米产品已经应用于该公司的智能手机‘Galaxy’。台积电(TSMC)的5纳米产品也得到了美国苹果公司智能手机和个人电脑的大量采用。”

——TSMC公布了年内量产3纳米产品的方针。

“随着微细化的发展,量产技术越来越难确立,不仅是日本企业,美国英特尔也掉队了,被韩台企业寡头垄断的情况日益加剧。TSMC的5纳米产品由于晶体管使用比硅更容易导电的硅锗材料,所以即使与三星的4纳米产品相比其性能也非常高。从技术竞争的角度来看,似乎没有急于推进大规模生产3纳米产品的必要性。今后将主要取决于三星的企业动向,(TSMC)有可能会战略性推迟3纳米产品的投放。”

——要想制造更高性能的半导体,什么将是最重要的?

“截止到三星的4纳米产品和TSMC的3纳米产品,晶体管都采用的是名为‘FinFET’的立体结构。三星宣布从3纳米产品开始,TSMC宣布从2纳米产品开始采用‘纳米片’结构。纳米片的量产技术目前尚未确立,都有哪些企业将会怎样制造备受关注。”

——率先实现纳米片结构的企业会不会垄断市场?

“集成电路的开发始终处于各公司相互竞争状态,一家公司单独拥有脱颖而出的独特技术的可能性几乎不存在。FinFET和之前的开发各家公司的步调也是基本一致的。”

“企业之间经常交叉授权专。各公司会累积在最新技术中各拥有多少专利,根据其数量相互支付费用。纳米片的开发应该也是这样。”

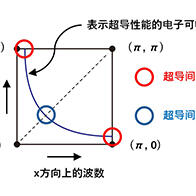

——硅结晶的最小单位为0.5纳米。微细化能达到什么程度?

“电路线宽低于5纳米左右时,就会发生名为隧道效应的量子力学现象。电子会穿过绝缘膜等,不再具有半导体功能。作为产品,微细化大约会推进到1纳米左右。”

——达到1纳米水平后,性能提升就会停止吗?

“还有通过堆叠晶体管形成双层构造来提高性能的技术。目前正启动各种智慧,研究微细化以外提高性能的方法。”

为不断变化的技术潮流做好准备

伴随着半导体已经微细化至数纳米程度,未来微细化的速度可能会放缓。日本已邀请TSMC在熊本县建立新工厂,但初期只量产略显落后于时代的20纳米级工艺产品。为了逐渐生产高性能半导体,日本还在继续推进招商,缩小与世界的差距非常重要。

另一方面,微细化接近极限的话,提高性能就要越来越多地依赖其他方法。堆叠半导体芯片形成三维构造的方法,以及将多枚芯片置于同一个封装中,作为一个产品发挥功能的“小芯片(Chiplet)”法都备受期待。

还有一种可能,各公司都使用自家的专用芯片。谷歌等美国科技公司已开始陆续开发自家芯片。日本需要做好准备及时应对全球技术潮流的变化,并提高存在感。

日文:大越优树、《日经产业新闻》,2022/6/6

中文:JST客观日本编辑部